#### **SMT Process Characterization and Financial Impact**

Fan Li Research In Motion Waterloo ON CA

#### Abstract

Portable Electronics devices are having more functionality but the size is getting smaller. What it means to SMT is to place more, smaller and ultra fine pitch devices on PC board. This makes SMT process capability the key measure to SMT quality. A number of the companies study the process capability at the time they evaluate or purchase the equipment, or at the time they design the product to fit the process capability. But process capability is changing over time. The process/machine was capable before may not be capable now.

The paper focuses on process capability and process control. It suggests process capability study should be a routine rather than a one time work. The paper is based on the practices in our company's manufacturing environment. For placement, the Cpk measurement was trialed on some of our lines. The measurement machine problem was analyzed and a proper measurement machine that fits the requirement was chosen. The Cpk result and product yield after proper calibration were very encouraging. For printing, a DOE was conducted based on the 0.4mm pitch BGA. The significant factors related to output of paste volume and paste deposit variation were found and an optimum setting combination was suggested to production. The process characterization has been proved to have a significant financial impact.

#### Introduction

Wireless technology today makes it possible to integrate more functionality to portable devices, like phone, PDA, email, camera and other entertainment such as music or even movies. The nature of potable devices that they are easy to carry and use. Lighter, smaller and thinner in size and larger in display is the trend for design. The requirements bring in challenges to SMT process like 0201, ultra fine pitch BGA, leadless QFN and LGA, high density. The use of RF shields make defect detect ability harder. Lead free solder for environmental legislation makes the situation even difficult.

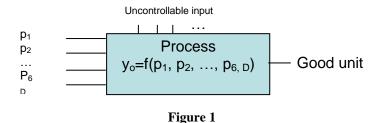

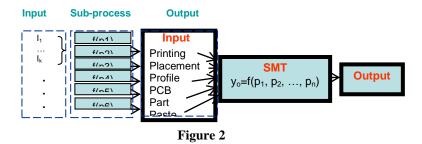

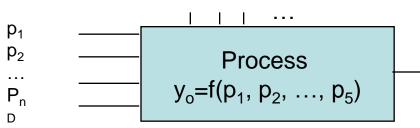

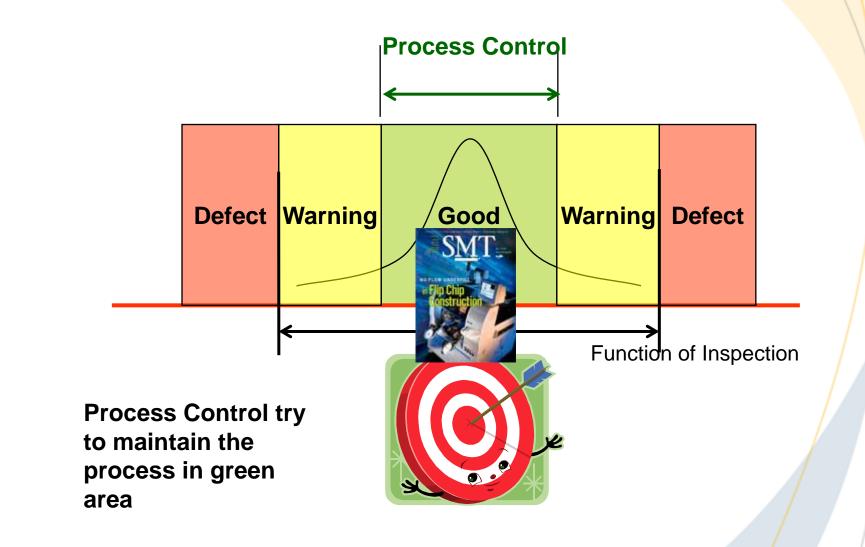

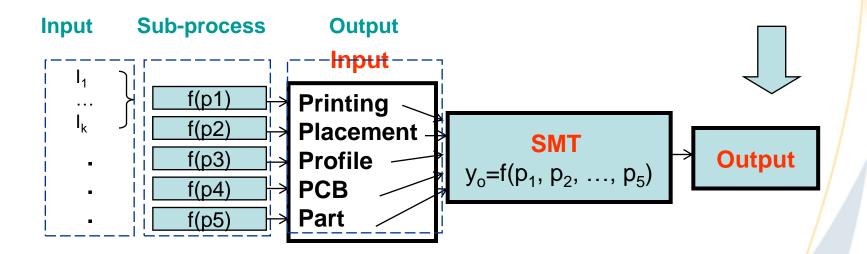

Before jumping to any solution, it is good to review the SMT process. If I put the major inputs of process as Printing, Placement, Profile, PCB, Paste and Part, that is 6Ps and put process design as another major input, the input would be 6Ps and 1D. These 6Ps and 1D we think are controllable inputs while some of the inputs are not controllable that are possible environment factors. Assume most companies try to keep the variation of the uncontrollable environment factors to minimum, so if 6 Ps and 1D are in control, the SMT process should be in control. For these 6Ps, the immediate factors we can control are placement and printing and profile.

For each high level input there is also a lower lever output of the process (shown below in Figure 2). For placement, the accuracy of part placement is considered one of the key factors to quality. For printing, the parameter setting and support setup are considered the key factors. For profile the ramping speed, peak temperature and time above liquidius. For PCB, besides design, the variation of solder mask, stretching, finishing etc are considered key parameters. Variation on paste and part will affect printing and placement accordingly.

**Process Characterization Practice**

#### 1. Placement Process Characterization

#### 1.1. Placement process and problem

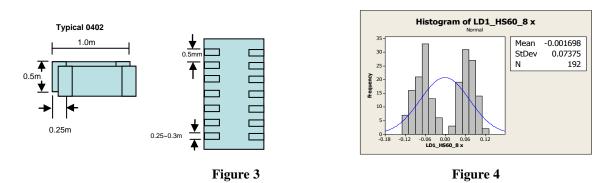

Placement accuracy is considered very important to placement quality. On most of the hand-held product, the size of the majority of the component is at the 0402 level and the BGA pitch is at the 0.5mm level. Referring to

Figure 3, if we look at 0402 part geometry, the size of terminal is  $0.5mm \ge 0.25mm$ , according to IPC standards If the part is offset by 50% of the pad which is 0.125mm, it is considered misaligned. This is also applicable for 0.5mm pitch BGAs. 50% of 0.25mm is 0.125mm and if the offset is more than 0.125mm it is considered misalignment. It is very reasonable to use +/-0.12mm as specification to measure the process capability. If standard of Cpk>=1.33 is applied to the capability study, it means that we have a very high confidence the process is capable for the placement. The +/-0.120mm was the specification we used on machine in RIM to test the placement machines. Very surprisingly we saw almost all Siplace machines failed the test. They all below the threshold of Cpk>=1.33 either in X or Y coordinate.

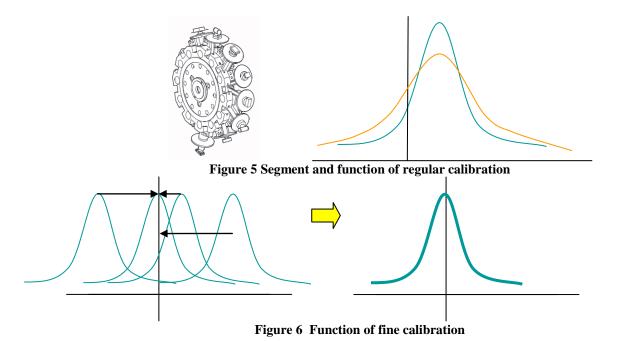

To investigate the causes behind this bad result, the distribution of the deviation of one of the machine was plotted. Obviously the distribution is Bimodal as showed above Figure 4. Continuing to

investigate the deviation of placement by each gantry was plotted. The distribution of each gantry was normally distributed but with an overall offset: two gantries shifted to left while the other two shifted to right. That was the reason that the distribution of the machines is not normal. When our investigation came to this conclusion that the machine needs calibration, the regular calibration was performed, but the result was not encouraging. Machine service was consulted. Another calibration called "Final calibration" was performed. This calibration brought the machine deviation data distribution to normal, and brought the Cpk to greater than the 1.33 threshold. Further investigation lead us to the knowledge that the two levels of calibration have difference focuses. Regular calibration focuses on segment calibration with the segment smaller showen in blue color. But it does nothing about gantry offset. Fine calibration focuses on gantry offset. Fine calibration checks the offset for each gantry and then the offsets are corrected to close to zero. (See Figure 6 Function of fine calibration).

#### **1.2.** Measurement system selection

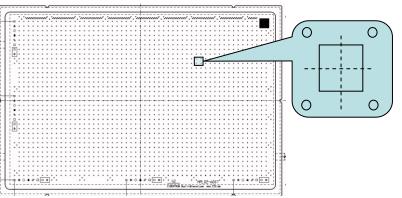

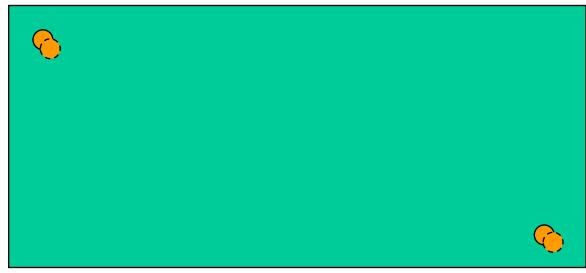

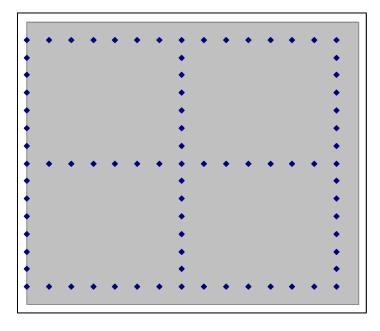

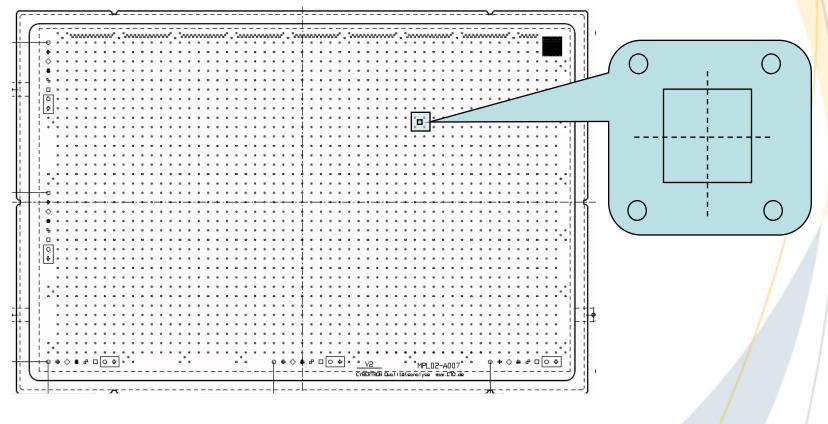

In the following weeks we saw the fine calibration was working well to correct gantry offset. But the "Fine Calibration" needs a long time which impacts production output. Deploying fine calibration in a busy manufacturing environment on a monthly basis may be a costly activity. To shorten the Checking or Calibration time, several methods were tried. Using AOI machine was tried. It was found that the accuracy of the AOI machine was not good enough to carry out the activity although the GR&R was good. Using an offline CMM machine and CeTaQ machine was tried too. For the placement Cpk check in particular, CeTaQ was considered the proper machine. The methodology of CeTaQ and "Fine calibration" are identical. Both using a grid glass plate which has a 3 um accuracy across the board (as shown in

Figure 7). Test components are placed close to the Dot (in the space among the 4 Dots) on the glass board. When measuring, the machine camera looks for the Dot(s) as a local fiducial(s) of which the coordinate is given. So the accuracy of the measurement pretty much relies on the accuracy of the glass board.

As mentioned the accuracy of the glass board is within 3 um across the board. To precede with the checking process, each gantry on each machine has been assigned with a number of placements to calculate the accuracy of the gantry. These components are then measured by the measurement machine offline without affecting production. The software provides detail information for segment and gantry. The calculated offset, if any, can be fed back to the machine data to make the machine pass the Cpk test.

#### Figure 7

#### 2. Printing Process Characterization

#### 2.1. Printing Problem

With more IO integrated a smaller package size is requested making the BGA have a smaller pitch. The problem we encountered was with the Ultra fine pitch BGA.

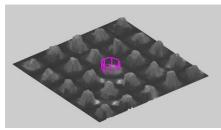

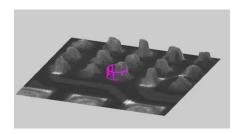

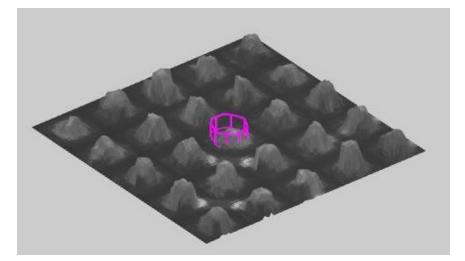

When the BGA was used on product, we saw insufficient solder (

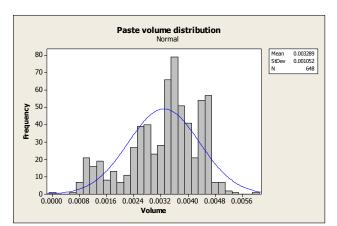

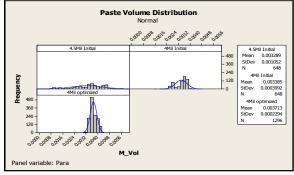

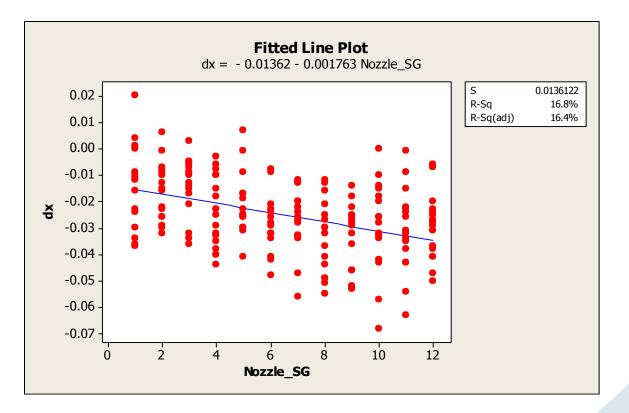

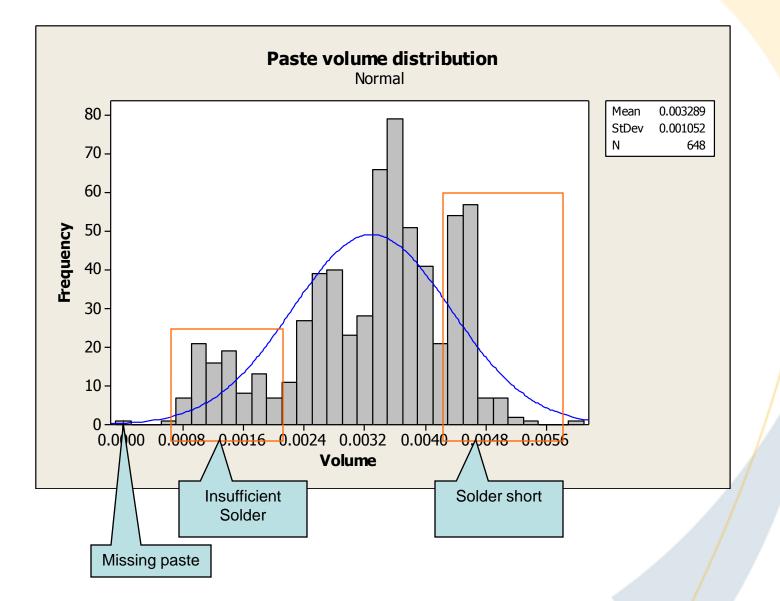

Figure 9) and excessive solder (Figure 8) on same BGA. When we measured the solder deposit volume after printing process, it is found that the variation was very large. (Figure 11).

#### 2.2. DOE and process optimization

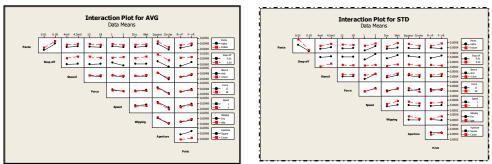

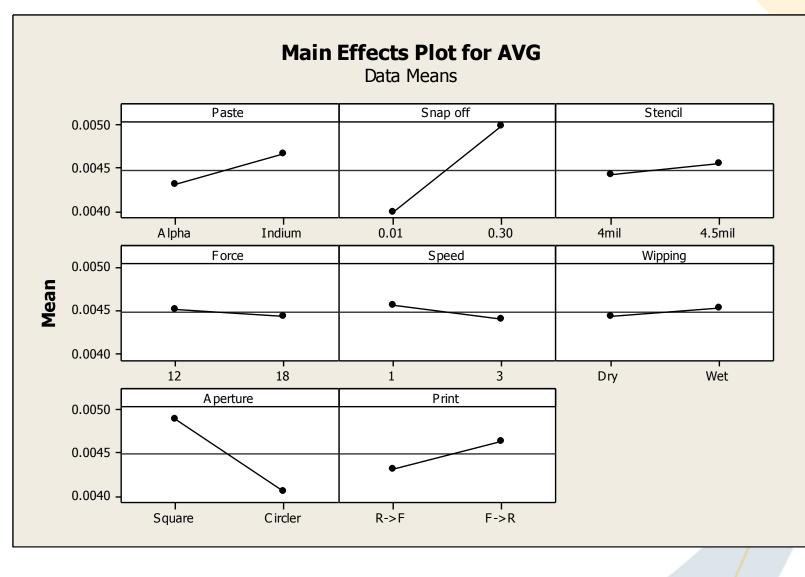

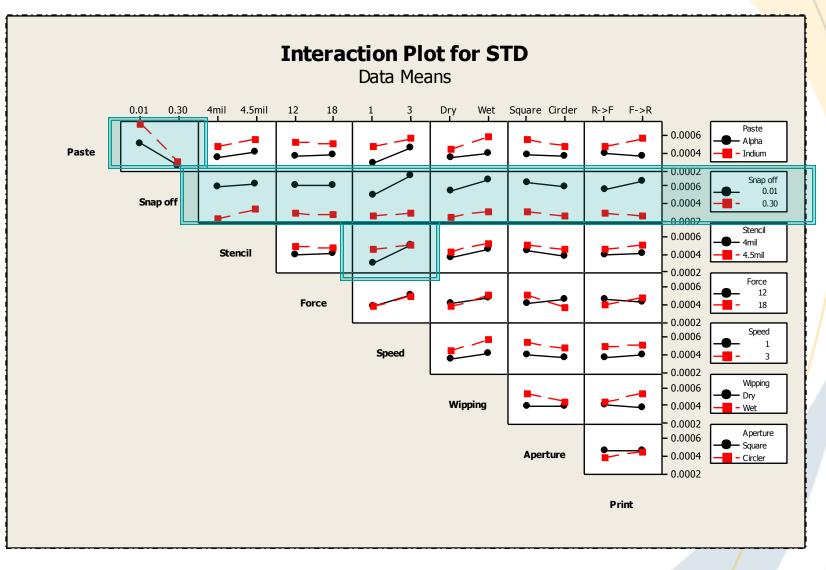

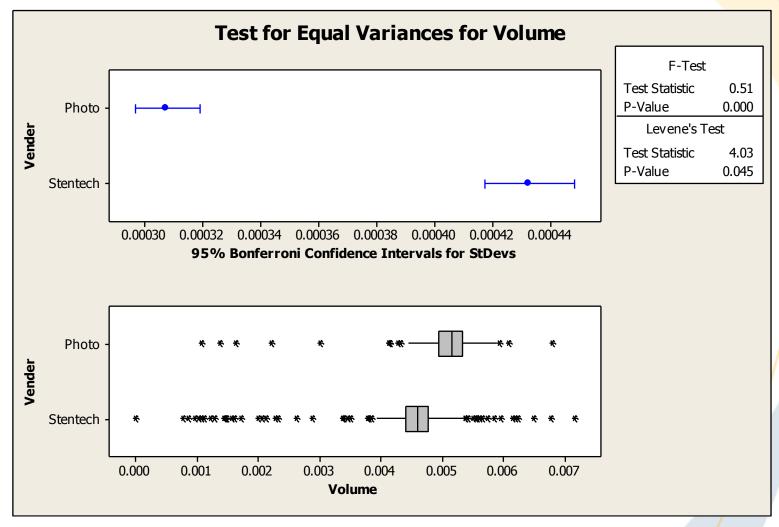

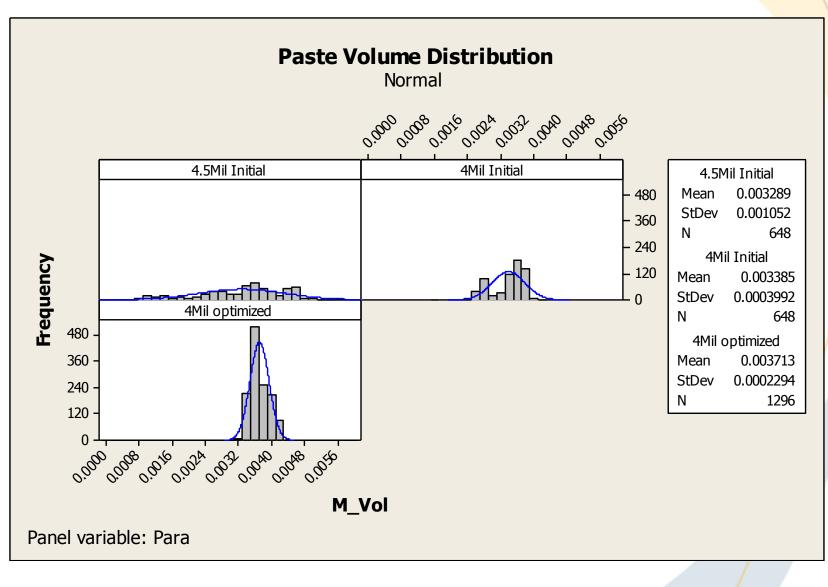

Digging into detail, there are two problems: one is the unstable printing process, another is the solder paste volume. Without stabilization of the process, any effort on stencil design change will not help the situation. So first we tried to reduce the variation and to get the process stable. With the input from paste manufacturer and printer supplier and also from process engineers, a DOE (Figure 12 DOE of printing process Average and Standard deviation) of 8 factors was planned to screen and optimize the factors. The output chosen are *Average* and *Standard Deviation* of the solder paste deposit volume. The *Average* is used to check the release performance of the paste. The *Standard Deviation* is used to check the stability of the process. The higher the volume average, the better the release performance. The smaller the standard deviation, the more stable the process.

Figure 11

#### Figure 12 DOE of printing process Average and Standard deviation

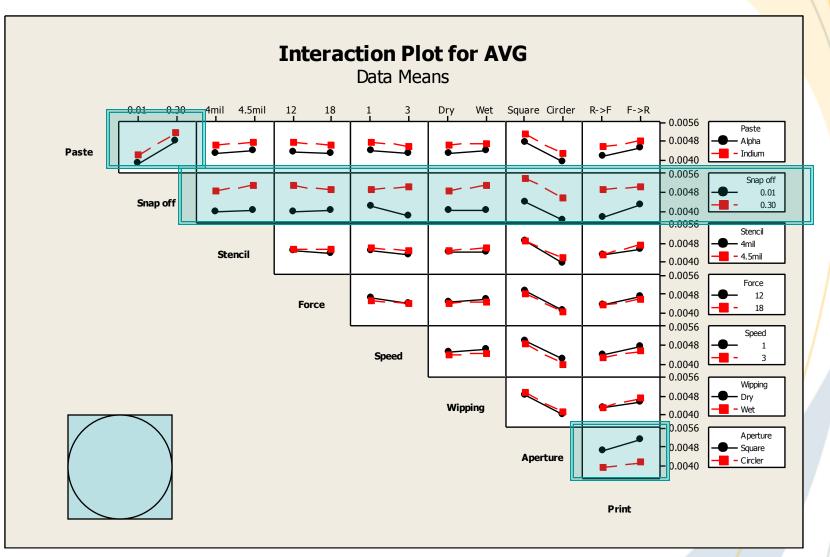

The DOE result suggests that the PCB-stencil separation speed is the most significant factor. Stencil thickness, aperture design and printing speed etc. have an impact on the output measured. But look at chart of interaction below. When PCB-Stencil separatation speed is set at the higher end of 0.3 inch per second, the difference on other factors (except for Aperture) tends to be flat on the chart. In other words, the difference from these factors is minimized.

Figure 13 Interaction of between factors

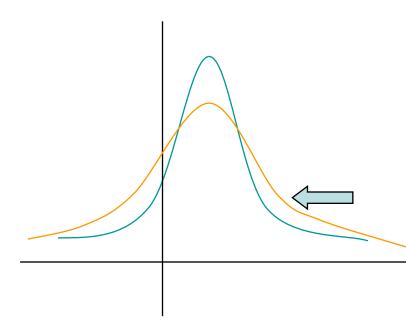

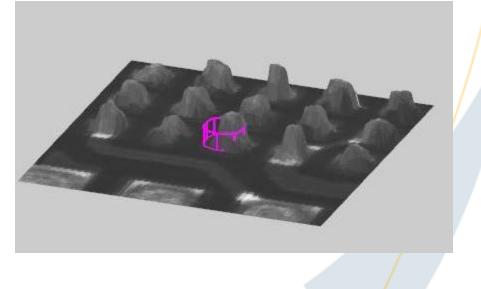

The confirmation run after the DOE also confirmed the result from analysis. In figure 13 the top left chart shows the same as in Figure 10. The bottom left chart is a 4 mil stencil with the best optimization. The distribution is narrow and tall. On real production, the defect of insufficient solder has been eliminated, but the solder short defect still exists. Further improvement involves aperture redesign and other factors.

Figure 14 Printing result comparison

#### 2.3. Other factors

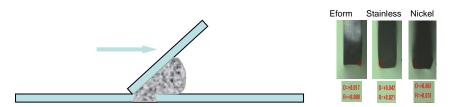

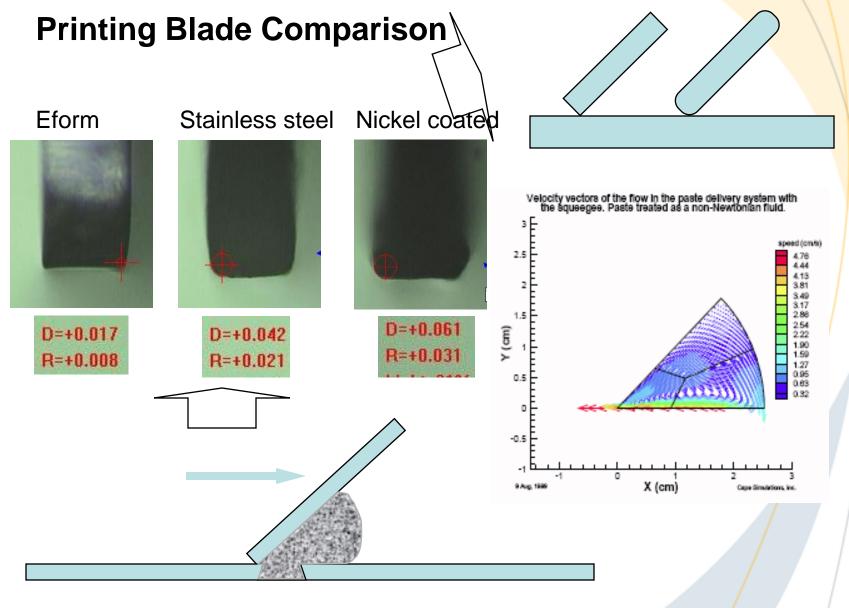

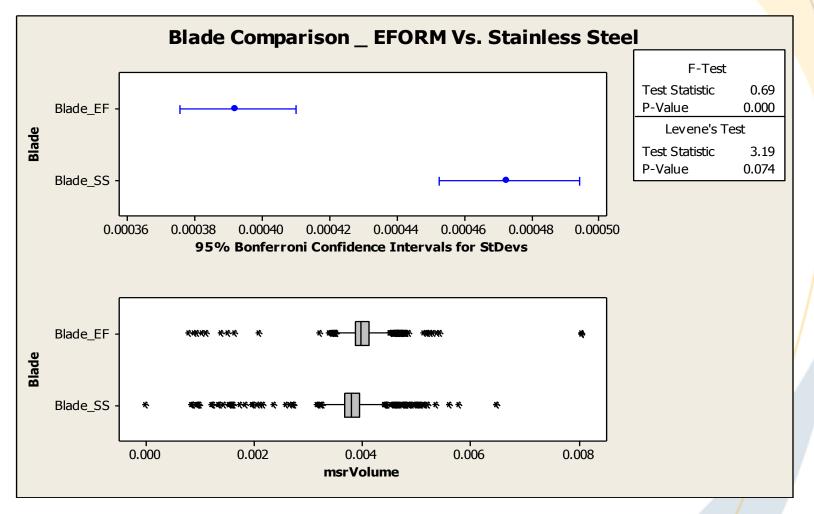

Besides optimization of printing parameters, other factor have been investigated: material of squeegee blade, stainless steel Vs. Eformed, PCB shrinkage and stencil stretching. The experiment shows the Eformed squeegee blade has a better result comparing to the stainless steel one. The reason would be the edge of the Eformed blade is sharper: it help in cutting process when printing. The surface of the blade is smoother which helps solder paste rolling on the stencil.

PCB shrinkage is another factor that affects the printing result. Although the shrinkage can be compensated in some degree in PCB manufacturing process by adding scale factor to the process, PCB shrinks further with every reflow. The worst case is that PCB is shrinking while the Eform stencil is stretching. With ultra fine pitch BGA, the process window for alignment is smaller than the stack of the tolerance. Efforts need to be made to get the PCB and stencil in control.

#### 3. Reflow

To some people reflow process may be considered very simple, but it is a very important process. Quality of the soldering is relying upon the process. Also some other defects may take place on this process too. Profile is a common character that every manufacturer controls. Normally the profile is done at very beginning. Each company has set a frequency to check the consistency of the profile. Physically running a profiler every day may be very expensive to some busy companies. We installed a KIC system to every oven to sample check the profile every hour for consistency. The variation can be read whenever it is needed. Any out of spec event generates a warning on the machine computer. Another important characteristic is the smoothness of the chains which are used to convey the board through oven.

If the smoothness of the chain movement is not good it may cause components movement when the solder become liquid. This is especially true for heavy components. Lubrication of chain should be treated as a important item for maintenance.

#### Summary

The financial impact through the process characterization was calculated with quality data and repair process analysis. The direct impact on yield was significant. The annual financial impact is on the million-level.

For any volume production, Characterization is the most effective way to improve the process quality and can have a direct financial impact. Without knowing the key parameters for the process and direction of adjustment, any effort on them could make the process worse. That was one of reason we saw that the process personnel kept adjusting the parameters every day but with the result that process varies over time.

# SMT Challenges and SMT Process Characterization

SMT Engineering Reaearch In Motion

By Fan Li

# Agenda

# □ SMT challenges □ SMT process overview SMT process characterization **≻**Placement > Printing **≻**Reflow Characterization Cycle

# SMT Oncoming Challenges

#### Challenges Requirement Smaller device, 0201 ٠ Ultra fine pitch uBGA, ٠ Placement Accuracy Leadless package QFN ٠ Printing reliability High density smaller spacing ٠ Reparability Leadfree soldering • <u>High SMT yield</u> **RF** shield • **-**Reflow High speed high volume production-• Others like Connectors, phone jack, ٠ **MIC** and Vibrator

# □ SMT Process Overview

Uncontrollable input

6Ps+1D in SMT process

- Printing

- Placement

- Profile

- PCB

- Part

- Paste

- Design

The 6 Ps+1D are the inputs for SMT, theoretically, if the 5Ps+1D are in control, the output more assured.

Good unit

SMT Process Overview

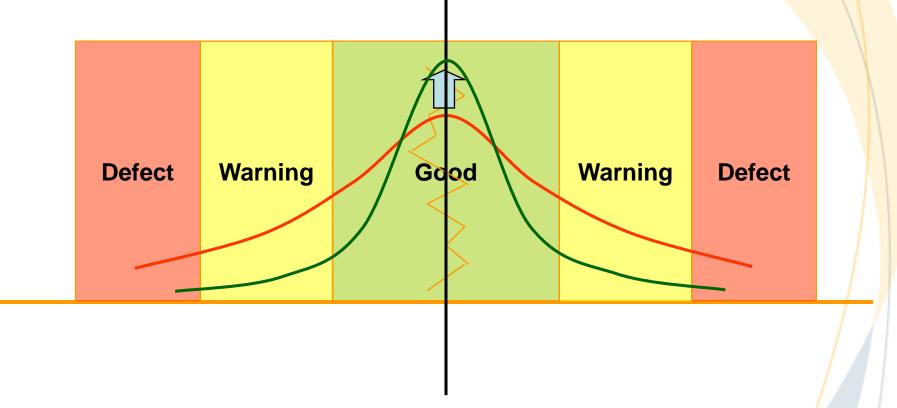

SMT Process Overview

The effort is to move from **RED** shape to **GREEN** shape

SMT Process Overview

- **Process Characterization focuses on inputs instead of output**

- Process Characterization focuses on sub-processes, even lower level processes

- □ If focus on output, when checking errors, problems already happened

- Focus on Input, try to control the input to control output, try to solve problem before it happens

# Placement\_Cpk

How the Cpk is measured and the Cpk result at the time

- A matrix of 0402 capacitors are placed on the IPC glass boards and the matrix was measured by Vi machine

- Vi GR&R was done with Spec. of +/-0.12mm and the GRR was less than 10%. GRR was good, but late on it was found that the accuracy of Vi was not good enough for Cpk study

- GRR result of Vi

| Spec.   | Source (Total<br>Gage R&R) | StdDev (SD) | (6 * SD) | (%SV) | (SV/Toler) |

|---------|----------------------------|-------------|----------|-------|------------|

| +/-0.12 | X                          | 0.0036705   | 0.022023 | 6.74  | 9.18       |

| +/-0.12 | Y                          | 0.0028767   | 0.017260 | 5.30  | 7.19       |

| 4       | Theta                      | 0.09056     | 0.54336  | 7.13  | 6.79       |

# Why choose 0.12mm as our Spec for X and Y

# Typical 0402 Chips 1.0 mm 0.5 mm 0.5 mm 0.5 mm 0.5 mm 0.5 mm 0.5 mm 0.25 - 0.3 mm 1.0 mm

## Future 0.08mm Spec is needed

# Where we were (Cpk at the beginning)

• Cpk result at that time was poor (See next slide)

|     |         | Historical Data |      |       |           |                   |      | HS50-1 | Fail | Fail | Р    | Fail | 09-M <mark>ar-07</mark>  |

|-----|---------|-----------------|------|-------|-----------|-------------------|------|--------|------|------|------|------|--------------------------|

|     |         | х               | Y    | Theta | Pass/Fail | Date<br>Performed |      | HS60-8 | Fail | М    | М    | Fail | 09-Mar <mark>-07</mark>  |

|     | 11000 4 |                 |      |       |           | 1 choimed         | LD1  | HS60-3 |      |      |      |      |                          |

|     | HS60-1  | Fail            | Fail | Fail  | Fail      |                   |      | HF3-1  | Fail | М    | Fail | Fail | 09-Mar- <mark>07</mark>  |

| LB1 | HS60-9  | Fail            | М    | Fail  | Fail      |                   |      | F5-1   |      |      |      |      |                          |

| LDI | HF3-5   | Р               | М    | Р     | Pass      |                   |      | HS60-  |      |      |      |      |                          |

|     | S20-2   |                 |      |       |           |                   |      | 10     | Р    | Fail | Р    | Fail | 15-Feb-07                |

| LB2 | S20-5   |                 |      |       |           |                   | LD2  | HS60-6 | Р    | Р    | Р    | Pass | 15-Fe <mark>b-07</mark>  |

| LC1 | HS60-5  | Fail            | Р    | М     | Fail      | 03-May-07         |      | HF3-3  | Fail | М    | Р    | Fail | 15-F <mark>e</mark> b-07 |

|     | HS60-4  | Р               | Р    | Fail  | Fail      | 04-May-07         |      | F4-1   |      |      |      |      |                          |

|     | S20-4   | Р               | Fail | Р     | Fail      | 05-May-07         | LE1A | HS60-2 | Fail | Fail | Fail | Fail | 16-Apr-07                |

|     | HF3-3   | Р               | Р    | М     | Pass      | 06-May-07         |      | HS60-7 | М    | М    | Fail | Fail | 16-Apr-07                |

| LC2 | HS50-3  | Fail            | Р    | P0    | Fail      |                   |      | HS50-3 | Fail | Fail | Р    | Fail | 16-Apr-07                |

|     | S20-2   | Fail            | Fail | Fail  | Fail      | 07-Mar-07         |      | HF3-2  | Ρ    | М    | Ρ    | Pass | 16-Apr-07                |

|     | HF3-4   | Fail            | М    | Fail  | Fail      | 07-Mar-07         | LE1B | HS50-2 | Fail | Fail | Fail | Fail | 16-Apr-07                |

| LC3 | HF3-6   |                 |      |       |           |                   |      | HF3-8  | Р    | М    | Fail | Fail | 16-Apr-07                |

# What happened?

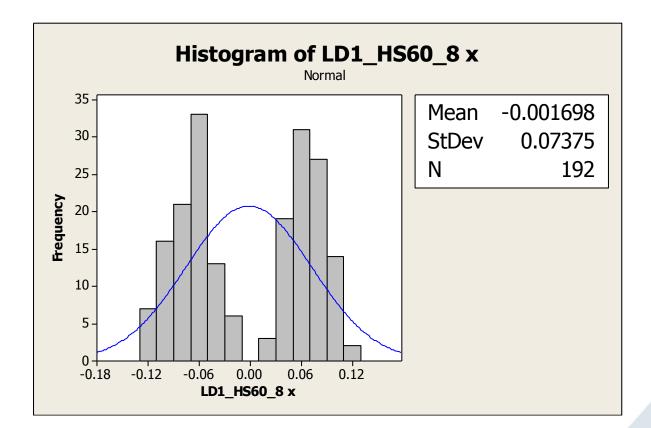

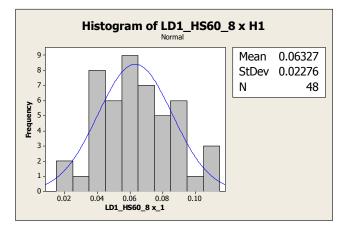

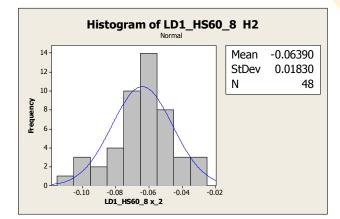

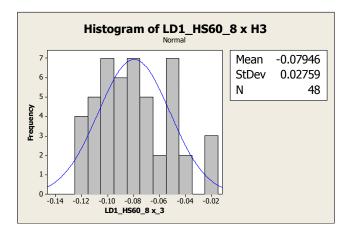

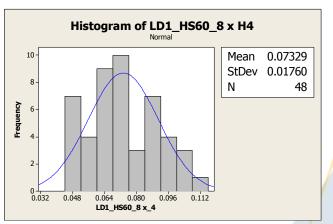

Example of HS60-8 in LD1 \_ Overall machine distribution graph

## Example of HS60-8 in LD1 \_ Distribution graph for each head

Distribution for each head seems Ok

48

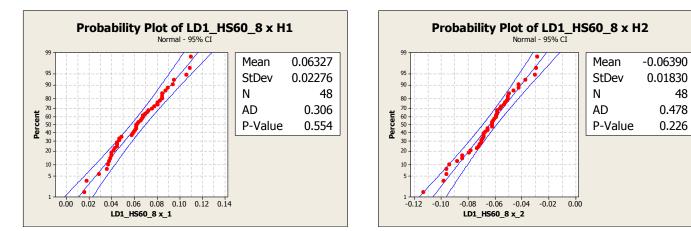

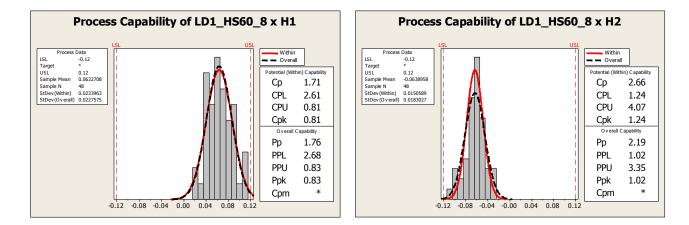

#### Example of HS60-8 in LD1 \_ Distribution Normality test graph for each head

Distribution for each head is normal

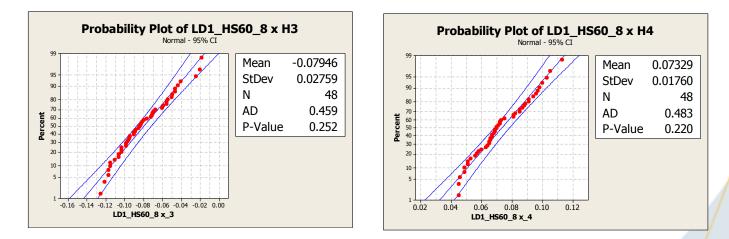

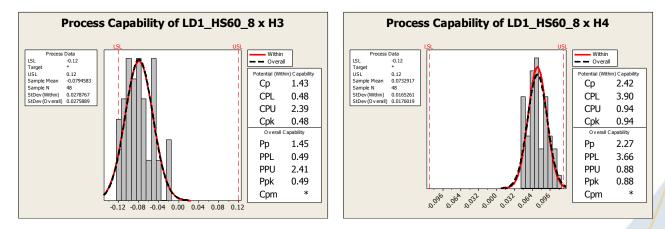

## Example of HS60-8 in LD1 \_ Cpk for each head

Cp for each head is Ok but Cpk not

**Machine offsets**

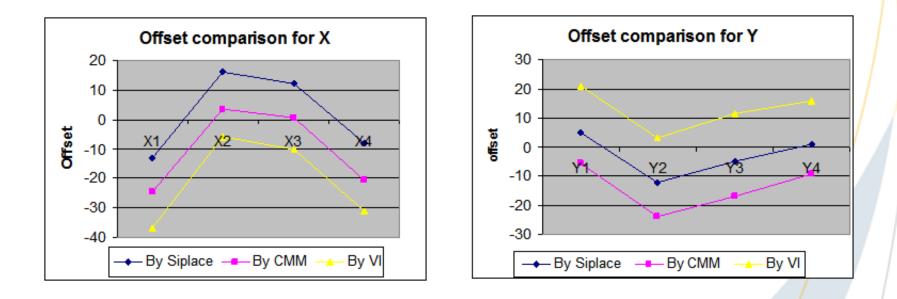

To verify the result and answer the concern raised by Siemens, the same glass plate was measured by three different machines, Siplace, CMM and Vi, and data was analyzed.

Result from three measurement system show similar pattern, but with offset in between. For this machine tested, head offset exists.

GRR on both Vi and Siplace shows a very good result, GRR on CMM was not satisfactory. So effort was focused on difference between Vi and Siplace.

From the analysis, Fiducial reading was considered the main reason that causes the offset. When look at machine setting, no threshold of fiducial reading can be set somewhere on the machine. When machine has a bad reading (not bad for machine to reject). The offset may occur

We have centralized database, every machine share the same fiducial data. But PCB cameras may have variations from machine to machine. The solution is to standardize the light setting on each camera

The effort following was to reduce the head offset

# What causes the problem and solution

- 2 Levels of the calibration

- Regular calibration

- Fine Calibration

Regular calibration focuses on segment offset

# What causes the problem and solution

\_ Continued

While Fine calibration focuses on Head offset to make the head offset close to 0

So the solution is to do both calibration to make a good Cpk

## **Result after both calibration**

After both calibrations, average offset on each head was within +/-5 micron, the Cm/Cmk measured from Siplace machine was good, but the result from Vi machine was not good as from Siplace machine. GRR was thought the major reason on one of two system

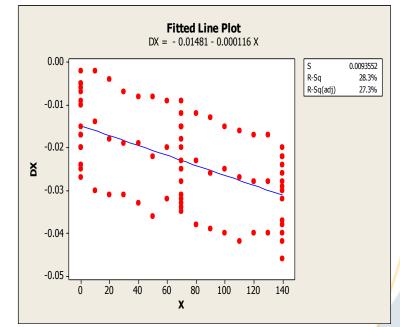

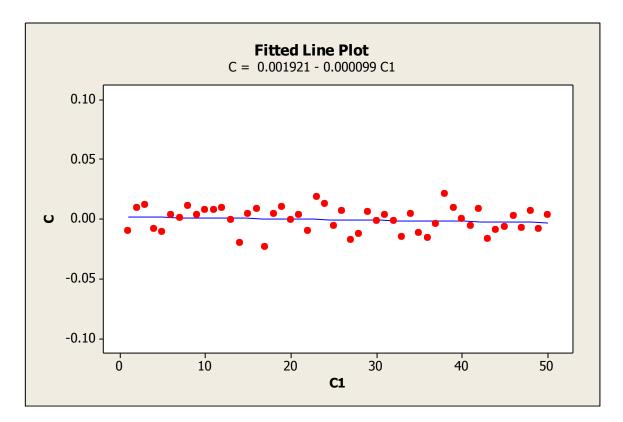

A regression graph for Vi was plotted to see possible problems, a trend of offset for each head was seen, but similar trend was not seen on Siplace measurement result

Vi accuracy was analyzed by using Vi machine to measure the Vi calibration glass plate. Conclusion from the plot

- The system has a offset range up to 45 microns

- The measurement residual is not random, the system has strong bias on location of measurement

- The system has a offset trend downward along with X

## Ideally, the plot of the measurement offset should be similar to the graph below

With the conclusion, we decided to use Siplace Fine\_cal system measure the machine Cpk

## Why trust Fine Cal System??

The accuracy of the measurement is major base on the accuracy of the glass plate more than accuracy of measurement machine. The local mark(dot) is checked prior to component check

# Project Result

Most the machines pass the Cpk test. The result was also used to replace the machines that are incapable to meet the requirement.

|     |              | ]  |       |     |       |           |           |

|-----|--------------|----|-------|-----|-------|-----------|-----------|

|     |              |    | Х     | Y   | Theta | Pass/Fail | Data      |

| LB1 | HS60-1       |    | Р     | Р   | NA    | Pass      | 18-Jun-07 |

|     | HS60-9       |    | Р     | Р   | NA    | Pass      | 18-Jun-07 |

|     | HF3_5        | RV | Р     | Р   | NA    | Pass      | 18-Jun-07 |

|     | пгз_з        | ю  | Р     | Р   | Р     | Pass      | 18-Jun-07 |

|     |              | RV | Р     | Р   | NA    | Pass      | 18-Jun-07 |

|     | HF3_4        | IC | F     | Р   | Р     | Fail      | 18-Jun-07 |

| LB2 | S20-5        |    | N/A F |     | NA    | Fail      | 13-Jun-07 |

| LC1 | HS60-5       |    |       |     |       |           |           |

|     | HS60-4       |    |       |     |       |           |           |

|     | S20-4        |    |       |     |       |           |           |

|     | HF3-7        |    |       |     |       |           |           |

| LC2 | X-1          |    |       |     |       |           |           |

|     | X-2          |    |       |     |       |           |           |

|     | F5-2         | RV | N/A   | N/A | Р     | Fail      | 19-Jun-17 |

|     | F0-2         | IC | Р     | F   | Р     | Fail      | 19-Jun-07 |

| LC3 | HF3-6        |    | Р     | Р   | NA    | Pass      | 25-Jun-07 |

|     | F5-3         |    | Р     | Р   | Р     | Pass      | 29-Jun-07 |

|     | го- <u>э</u> |    | Р     | Р   | Р     | Pass      | 29-Jun-07 |

S20 in LB2 and F5 in LC2 has mapping problem, but mapping process failed with several attempts on LB1

Г

Placement

| LD1  | HS50-1  |    | Р | Р   | NA | Pass | 6/7/07(6/26) |                      |  |

|------|---------|----|---|-----|----|------|--------------|----------------------|--|

|      | HS60-8  |    | Р | Р   | NA | Pass | 7-Jun-07     |                      |  |

|      | HS60-3  |    | Р | Р   | NA | Pass | 7-Jun-07     |                      |  |

|      | HF3-1   |    | Р | Р   | NA | Pass | 7-Jun-07     | HF3-3 in             |  |

|      | F5-1    |    | Р | Р   | NA | Pass | 7-Jun-07     | LD2 has a            |  |

|      | HS60-10 |    | Р | Р   | NA | Pass | 6-Jun-07     | distribution         |  |

| LD2  | HS60-6  |    | Р | Р   | NA | Pass | 6-Jun-07     | other than<br>normal |  |

|      | HF3-3   |    | Р | N/A | NA | N/A  | 11-Jun-07    |                      |  |

|      | F4-1    |    | Р | Р   | NA | Pass | 6-Jun-07     |                      |  |

|      | HS60-2  |    | Р | Р   | NA | Pass | 2-Jul-07     | IC head on           |  |

|      | HS60-7  |    | Р | Р   | NA | Pass | 2-Jul-07     | HF3-2 has a          |  |

| LE1A | HS50-3  |    | Р | Р   | NA | Pass | 2-Jul-07     | larger<br>variation  |  |

|      | HF3-2   | RV | Р | Р   | NA | Pass | 2-Jul-07     | the twin             |  |

|      |         | IC | F | Р   | F  | Fail | 2-Jul-07     | head may             |  |

| LE1B | HS50-2  |    | Р | Р   | NA | Pass | 2-Jul-07     | need to be           |  |

|      | HF3-8   | RV | Р | Р   | NA | Pass | 2-Jul-07     | changed              |  |

|      |         | IC | Р | Р   | Р  | Pass | 2-Jul-07     |                      |  |

# **Printing DOE**

For better release and consistency of the release

Printing

# Inspection result from Orbotech

## Insufficient solder paste

Solder paste height too high

Printing

# **Correlation between paste deposit and solder defect**

# Base on the knowledge from SMT group and recommendation from solder paste supplier. The following factors are considered

- Solder paste \_ Alpha vs. Indium

- Stencil aperture design 0.25mm Circular vs. 0.25mm square

- Thickness of stencil \_ 4mil vs. 4.5mil

- Printing snap off (stencil separation speed) \_ 0.3"/s vs. 0.01"/s

- Printing speed \_ 1"/s vs. 3"/s

- Printing force \_ 12lb vs. 18 lb

- Wiping effect \_ Wet vs. Dry

- Printing stoke \_ To rear vs. From rear

The DOE is combination of screening and optimization DOE. It is to weed out the factors that have little impact to printing result and also to seek a parameter combination to make the printing result robust

The output of the DOE was define the average paste volume and standard deviation

#### **DOE result** \_ Main effect of each factor for solder paste volume

**DOE result** \_ Interaction between factors for solder paste volume

**DOE result** \_ Interactions between factors for solder paste standard deviation

## **Stencil Comparison**

Photo stencil gives significant lower variation on paste and fairly larger volume

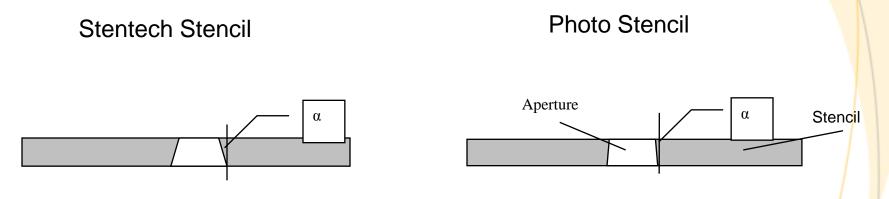

## **Stencil Fabrication Comparison**

Idea angle for  $\alpha$  is 1~3 degree For stencil 1,  $\alpha$ =6~7 degree, for stencil 2  $\alpha$  close to 0 degree.

Clarification: Here is not to compare the quality of two manufacturers, they are used to see the relationship between release performance and taper angle. Stentech process has a good control on thickness and it also has made process change on taper angle.

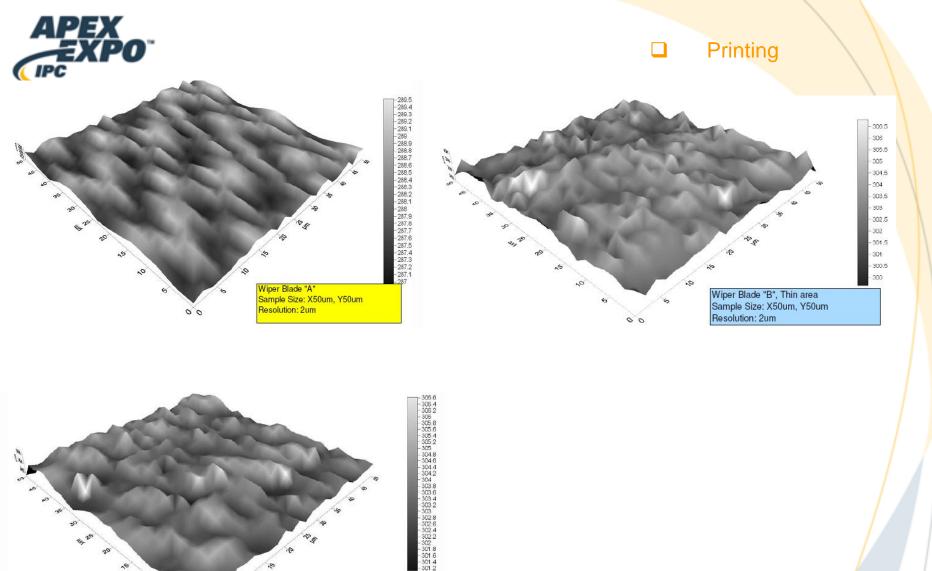

Wiper Blade "B", Thick area Sample Size: X50um, Y50um Resolution: 2um

#### **Results:**

3 Wiper Blades (A-Pure Nickel, B-Pure Stainless Steel, C- Nickel-coated Stainless Steel) were checked for Surface Finish/Roughness (used Cyberscan), Work Edge radius (used CMM) and Thickness (used micrometer). Please see pictures, below, for detailed views.

**Wiper Blade "A"** had a wavy surface pattern with distance between valleys and peaks of 3 microns. Blade radius was only at corners (8 micron radius) with flat bottom. Blade thickness was 150 microns.

**Wiper Blade "B"** had mostly random surface pattern, some slight striation, with distance between valleys and peaks of 8 microns. Blade radius was only at corners (20 micron radius) with flat bottom. Main blade thickness was 300 microns, while on step it was 180 microns thick.

**Wiper Blade "C"** had mostly random surface pattern, some slight striation, with distance between valleys and peaks of 7 microns. Peaks appear to have sharper points than "A" and "B". Blade radius was only at one corner (30 micron radius) with flat bottom and 60 degree chamfer on the other edge (Working edge). Blade thickness was 270 microns

#### **Blade Comparison**

Eform blade has a significant smaller variation, and non-significant larger volume

#### Printing Result Comparison

#### Something to be continued for printing...

#### Fact

PCB shrinks while Eform stencil stretches

#### Stencil

- Stretch of Eform process

- Thickness of foil for stencil for Eform process

- Taper angle of the aperture

- Stencil fiducial accuracy

- Laser cut Eformed foil?

- New laser cut process?

#

- Simple? important

- Consistency of reflow machine,

- Chain smoothness

- Parallel of two chains

- Circulation fan speed

- Variation of of profile. Hourly check by KIC

# Characterization Circles

- Machine Accuracy

- Printing performance

- Profile control

- Camera Cal

- Stencil design

- Parameter optimization

- GF and nozzles

- Accuracy

. . . .

### Acknowledge and thanks

### Special thanks to

- Jay House for the help on Cpk execution on placement

- Anthony Xue and Jack Han for the Printing DOE design and execution

- Jamie Topping from Siemens for Cpk trials

- Frank Andres from Alpha and Edward H. Briggs from Indium for the printing DOE trial

- Willie Henderson for the support of the project

# **Question?**